次世代ウエハ積層技術に世界ではじめて成功研究成果

次世代ウエハ積層技術に世界ではじめて成功

|

1.タイトル:「次世代ウエハ積層技術に世界ではじめて成功」

2.発表概要:

東京大学大学院工学系研究科附属総合研究機構(東京都文京区弥生2-11-16、機構長寺井隆幸)は株式会社ディスコ、大日本印刷株式会社、株式会社富士通研究所などと共同で、最先端半導体シリコン基板(ウエハ)を何層でも積層することができる技術開発に世界で初めて成功した。同成果は半導体における国際会議AMC2008で報告される。

3.発表内容:

ナノテクノロジーの最先端を走る半導体では、微細化の限界から、半導体チップを三次元化することで高速性やメモリ容量を向上させることが必要となってきている。この三次元化技術は、実用化されるとMEMSバイオチップ、MEMSセンサーなどとも組み合わせが容易になり、新市場を創出する次世代システムチップの基盤技術として期待がもたれている。

これまで、半導体チップの積み重ねや、ウエハにチップを載せる手法では既存のウエハプロセス技術とは異なるため、生産性が低くコストが高くなる課題があった。今回、ウエハ単位で簡単に積層できる三次元化技術を、東京大学附属総合研究機構ナノ工学研究センター大場隆之特任教授を中心に株式会社ディスコ、大日本印刷株式会社、株式会社富士通研究所など複数企業からなる産学アライアンス(通称ワウ(WOW)アライアンス、WOW Alliance = Wafer-on-a-Wafer Alliance)が世界ではじめて技術開発に成功した。同技術では、シリコン基板の厚さを予め薄くし、積層した後にウエハとウエハを貫通シリコン電極によって配線するセルフアライン(自己整合)方式を用いている。

この方法を用いることで、これまでの課題であった深いシリコンエッチング加工が必要なくなり、応力が軽減される為、必要に応じてウエハを何層も重ねることが可能となる。また、ウエハ単位で処理できることから、半導体ウエハプロセス技術(前工程)および半導体製造装置の応用が容易になり、半導体ウエハプロセス製造と同様な大量生産が可能となる。大量生産が可能になると、量産効果でコストが下がり、半導体市場で十分なコスト競争力を得ることができる。さらに、マイクロプロセッサーの積層、例えば既存世代のマルチコアを積層すれば、性能を損なうことなく消費電力を低くすることができ、メモリの積層、例えば16GBのフラッシュメモリーウエハを10枚重ねてチップ状にすれば、超小型で160GBの大容量メモリを容易に製造することができることになる。

同産学アライアンスでは、現在のところ7層ウエハの積層に成功しており、本年9月にサンディエゴで開催される国際会議(Advanced Metallization Conference、通称AMC)で詳細を報告する予定である。

4.発表:Advanced Metallization Conference国際会議

5.注意事項:特に無し

6.問い合わせ先:

東京大学大学院工学系研究科附属総合研究機構

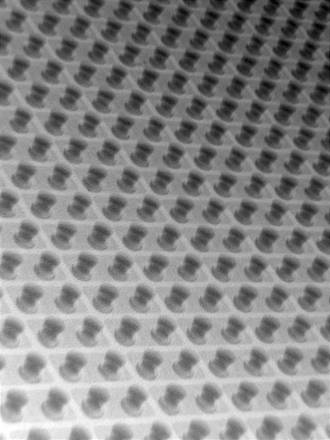

7.添付資料:本技術で形成した基盤をつなぐCu埋め込み配線をエックス線で観察した結果。Cu埋め込み配線は、Si貫通孔(TSV: Through Silicon Via)を通して自己整合(セルフアライン)的に形成された。