量子コンピュータのノイズ効果を抑制する量子誤り抑制法の原理的性能限界を解明研究成果

2023年11月23日

東京大学

電気通信大学

科学技術振興機構(JST)

発表のポイント

- ノイズのある量子コンピュータへの適用が期待されている量子誤り抑制法の原理的性能限界を明らかにした。

- 量子誤り抑制法の一般理論を導入することで、従来のケースバイケースの解析では不可能であった普遍的な性能限界の解析に初めて成功した。

- 量子誤り抑制には量子回路の深さについて指数的な時間コストが必ず必要となることを証明した。本研究の結果は、有用な量子コンピュータの実現を考える上での将来的な指針を与えるものと期待される。

発表概要

東京大学大学院総合文化研究科の高木隆司准教授、電気通信大学大学院情報理工学研究科の田島裕康助教(兼任:科学技術振興機構(JST)さきがけ研究員)、Nanyang Technological University SingaporeのMile Gu准教授による研究グループは、量子コンピュータ(注1)におけるノイズ効果を抑制する方法として注目されている「量子誤り抑制法」(注2)に課される普遍的な性能限界を、量子力学の原理から明らかにしました。

量子技術の実験的発展が目覚ましい今日、ノイズがある小・中規模の量子コンピュータの計算性能を理論的に特徴づけることは大きな課題となっています。本研究では、どのような量子誤り抑制法に対しても普遍的に必要となる時間コストを導出し、特に量子回路の深さ(注3)に対して時間コストが指数的に増大することが原理的に避けられないことを初めて証明しました。この結果は今後の量子技術の発展の方向性の指針を与えると同時に、本研究によって導入された、ノイズのある量子系の操作的性能を情報理論の側面から明らかにする研究アプローチの将来的な発展が期待されます。

本研究成果は、2023年11月22日(米国東部時間)に米国科学誌「Physical Review Letters」のオンライン版に掲載されました。

発表詳細

大学院総合文化研究科のページからご覧ください。

用語説明

(注1)量子コンピュータ:量子力学の原理を用いて計算処理を実行するデバイスで、化学や機械学習等の分野への応用が期待されている。

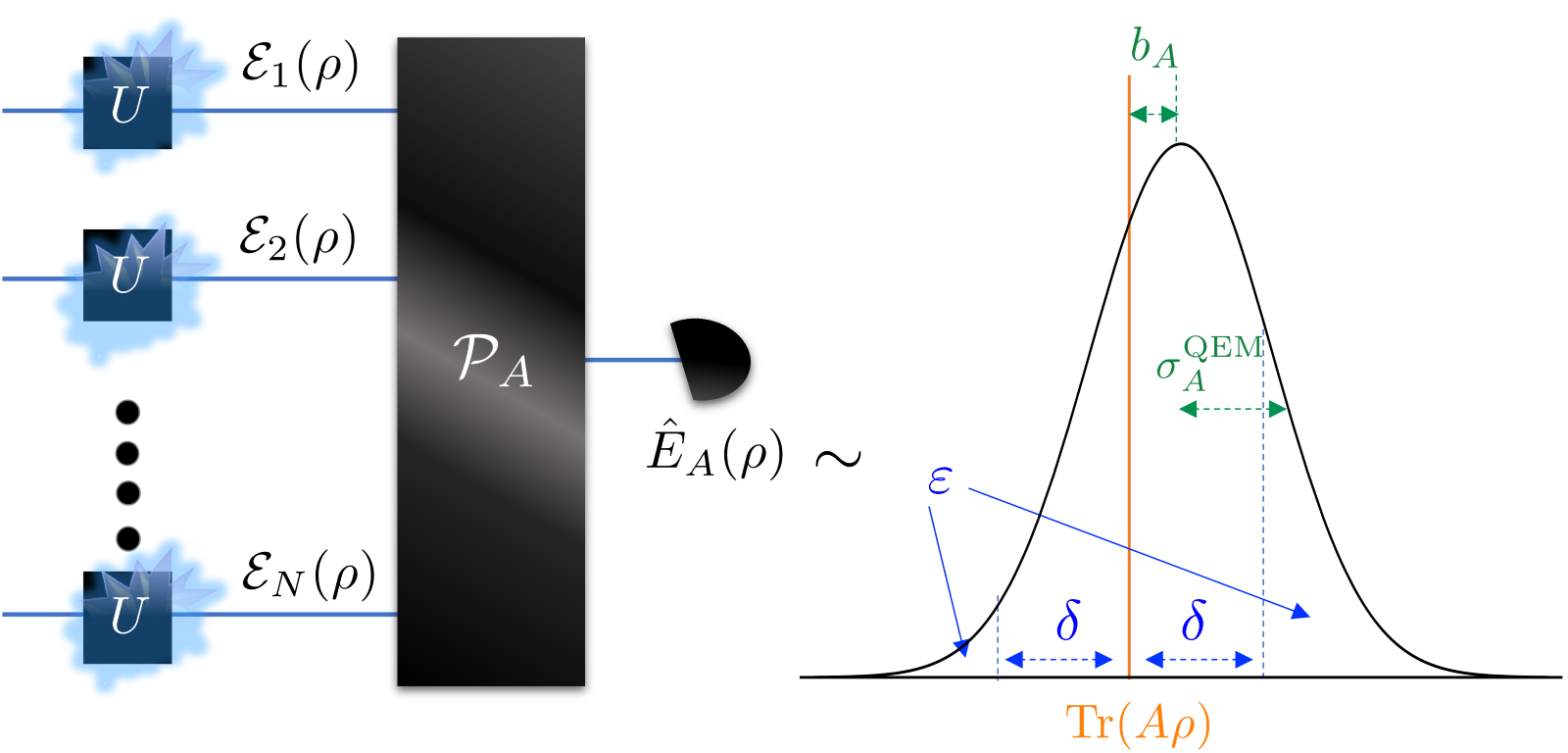

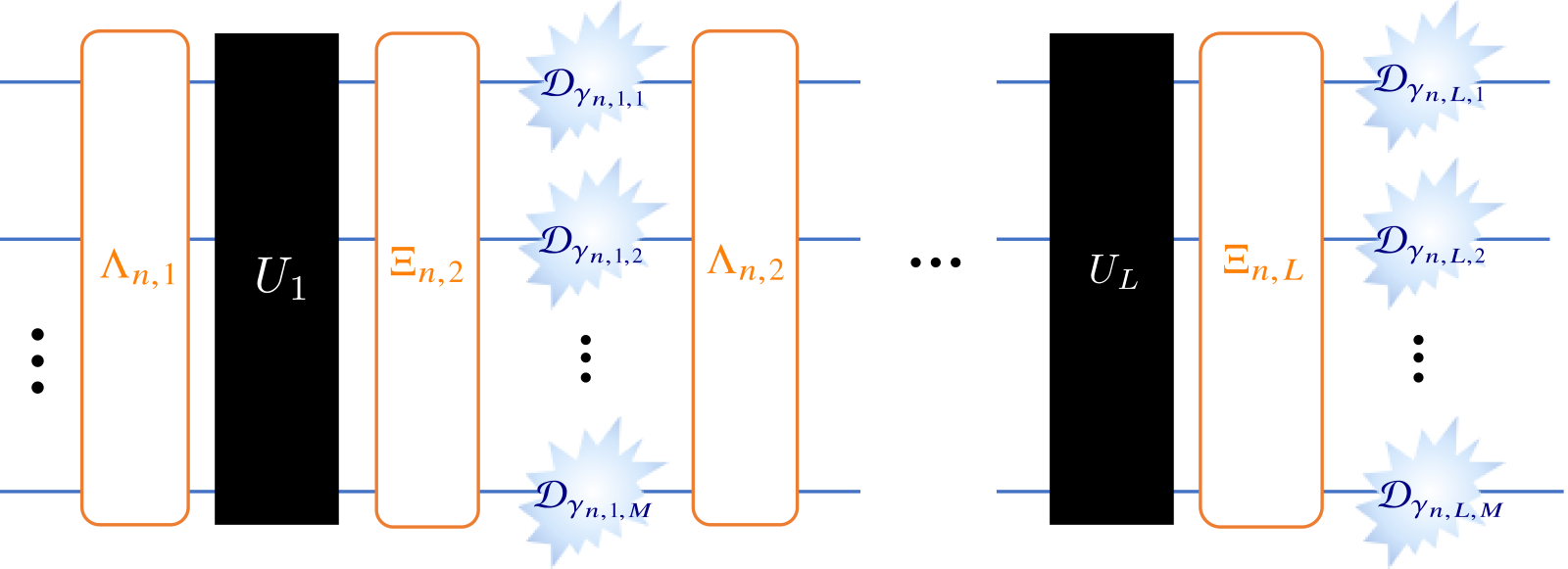

(注2)量子誤り抑制法:ノイズの存在下において量子計算の計算精度を保証する方法として量子誤り訂正法が提唱されているが、それに必要な量子誤り訂正符号を実装するためには大規模で高精度な量子コンピュータが必要となる。量子誤り抑制法は、量子状態を符号化する代わりに量子計算を多数回繰り返した後古典的な情報処理を加えることによって計算精度を高める方法で、近年実現されてきている小・中規模の量子コンピュータに適用可能な方法として注目を集めている。

(注3)量子回路の深さ:量子計算は量子ゲートと呼ばれる演算を量子状態に次々と適用させていくことで実行される。どのように量子ゲートを適用するかを表すものは量子回路と呼ばれ、それらの量子ゲートを適用するのに必要な総時間ステップ数は量子回路の深さと呼ばれる。

論文情報

Ryuji Takagi*, Hiroyasu Tajima, and Mile Gu, "Universal Sampling Lower Bounds for Quantum Error Mitigation," Physical Review Letters: 2023年11月22日, doi:10.1103/PhysRevLett.131.210602.

論文へのリンク (掲載誌 )

)

関連リンク

- 本研究結果と同時に発表された関連論文に関するプレスリリース 「量子コンピュータのエラー抑制技術の理論限界を解明 ――最適な量子エラー抑制手法の設計に向けて――」

- 東京大学 大学院総合文化研究科

- 高木隆司研究室